OpenRISCはOpenCoresコミュニティの元々の旗艦プロジェクトである。 このプロジェクトの目的は、一連の汎用のオープンソースのRISC CPUアーキテクチャを開発することである。最初で現在のところ唯一のアーキテクチャは、OpenRISC 1000である。これは、 32ビットと64ビットがあり、オプションとして浮動小数点演算とベクトル演算を持つファミリである。

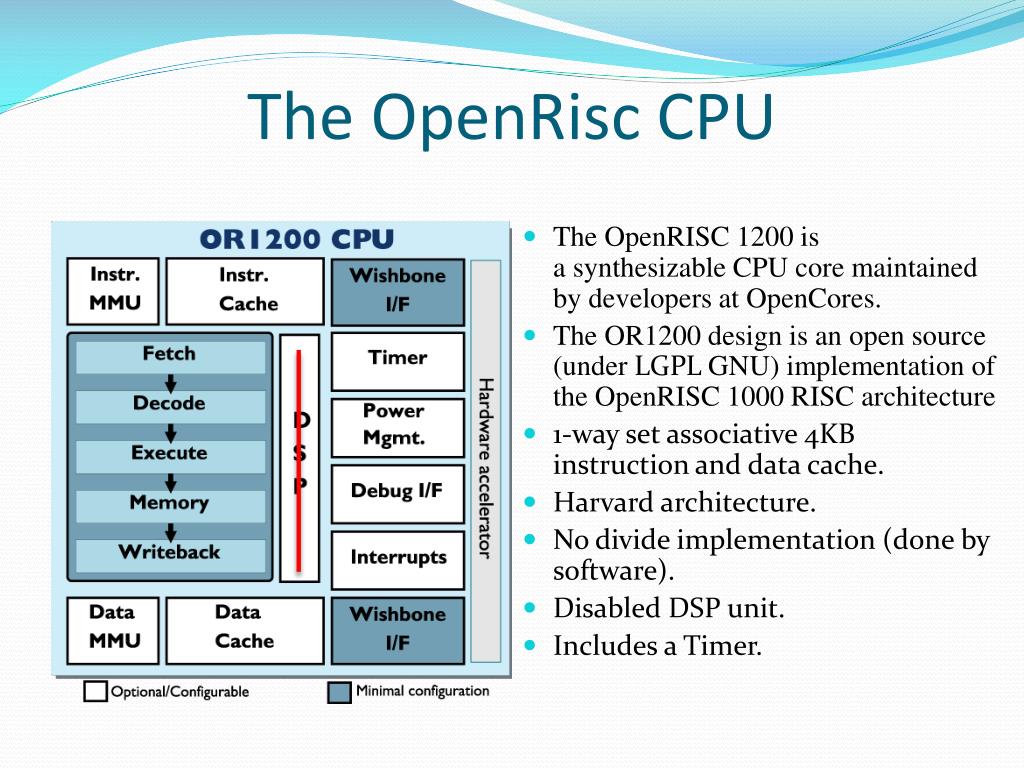

OpenCoresのチームは最初の実装であるOpenRISC 1200を提供している。これはVerilogハードウェア記述言語で書かれている。ハードウェアのデザインは、GNU Lesser General Public Licenseでリリースされたが、モデルとファームウェアはGNU General Public Licenseでリリースされた。リファレンスのSoCの実装はOpenRISC 1200ベースで開発され、ORPSoC (the OpenRISC Reference Platform System-on-Chip)として知られている。ORPSoCや他のOpenRISC 1200ベースのデザインのデモンストレーションをしたグループは、FPGA上で動かしていた。.

商業的な実装

いくつかの商業組織によってOpenRISC 1000アーキテクチャの派生物が開発されている。ORSoC による ORC32-1209 や Beyond Semiconductor による BA21、BA14、BA22 がある。ORSoCはopencores.orgウェブサイトを維持している。Dynalith Systemsは、OpenRISC 1000とBA 12の双方を使えるiNCITE FPGAプロトタイピングボードを提供している。Flextronics InternationalとJennic Limitedは、ASICの一部としてOpenRISCを製造している。

ツールチェーンのサポート

OpenCoresコミュニティはC言語での開発ができるようにした。GNUツールチェーンをOpenRISCに移植した。このツールチェーンを使うことにより、uClibcやLinux、μClinuxも移植された。Dynalith Systemsは、このツールチェーンをベースとしたグラフィカルな開発環境であるOpenIDEAを提供している。

OpenCoresコミュニティは、OpenRISC 1200とORSoCの両方の命令セットシミュレータとサイクル精度モデルを提供している。OpenRISC 1200の高速のモデルも、Imperasにより主導されたOpen Virtual Platforms (OVP)を通して入手できる。

脚注

関連項目

- OpenRISC 1200

- OpenCores

- Open Virtual Platforms

- OpenSPARC

外部リンク

- OpenRISC 1200 についての Open Cores ホームページ (英語)

- GNU ツールチェーン構築ガイド (英語)

- Beyond Semiconductor OpenRISCの開発者によって起業されたファブレス半導体企業。(英語)

- Dynalith Systems 日本語のパンフレットの PDF ファイルを配布。

- Imperas 企業ホームページ。(英語)

- Flextronics International 企業ホームページ。

- Jennic 企業ホームページ。(英語)

- ORSoC 企業ホームページ。 ORSoCはopencores.orgホームページも維持している。(英語)